3D IC封装:超高密度铜-铜异质接合

陈智 教授

博士生:刘纮哲

台湾阳明交通大学 材料科学与工程学系

消费性电子产品与车用芯片的需求日益提高,半导体产业芯片效能被大幅提升。当工艺迈向 3 纳米,摩尔定律走到极限,先进封装整合是突破的关键?

根据摩尔定律预测,每 18 个月芯片内部单位面积的晶体管数量将会翻倍成长,此预测在 2020 年已达到 5 纳米节点量产,接着需要开发 3 纳米节点的量产工艺,其生产成本大幅提高,有专家因此预测摩尔定律往后将受到物理极限限制,或因成本考虑而难以延续。

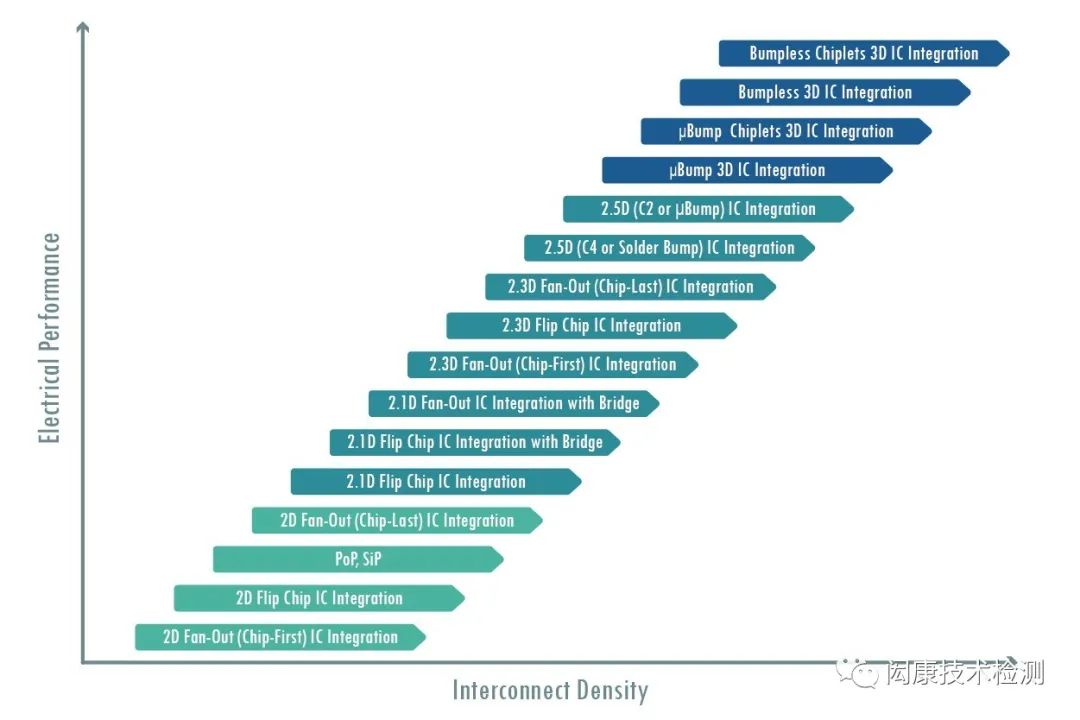

有许多研究者提出了新的解决方案,利用其他技术来提升芯片效能,并将之后称为「后摩尔时代」,其中最引人瞩目的方案为异质整合 (Heterogenous Integration) 与小芯片 (Chiplet) 技术。异质整合技术为将不同的功能芯片利用 2.5D/3D 封装技术整合在一起,获得多功能芯片;而小芯片技术为将相同功能或将大芯片拆成小芯片个别提升效能后,再利用封装技术整合在一起,图一为专家预期利用不同封装技术可以使芯片效能提升的排名[1]。这两个解决方案的关键为先进封装 (Advanced Package) 技术,因此需要专家与厂商针对 2.5D 与 3D 封装技术投入大量心力。

图一 芯片性能表与接点密度先进封装排名表[1]

异质整合封装技术相较传统封装具备高度芯片整合能力,拥有超小接点尺寸与间隙的优势,能够大幅减少多层芯片的堆栈厚度,被视为是延续半导体工艺最重要的发展动能。

封装技术的演进最早为打线接合 (Wirebond),由于其接点仅能以周列形式排列在芯片周围,无法有效提高接点的 I/O 数量,因此 IBM 提出了覆晶接合 (Flip Chip),利用焊锡微凸块 (Solder Bump) 当作接点将芯片与芯片接合在一起,接点为数组式排列,可以分布于整个芯片上,并且将焊锡凸块尺寸微缩,即可以非常有效的提高接点 I/O 数量。

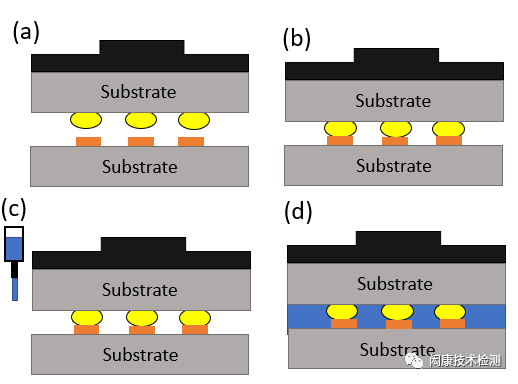

覆晶焊锡接合过程如图二所示,接合时利用无铅焊锡与铜的低熔点特性,使接点在约 230 ℃ 下形成稳定接点,接着再将底部填充剂 (Underfill) 填满接点之间的间隙,提高接点机械性质。当接点间距 (Pitch) 微缩至 10 微米左右时,将会出现许多问题,例如:接点越小焊锡球尺寸也会缩小,容易将焊锡球完全反应形成金属间化合物 (Intermetallic Compound, IMC) 接点,IMC 接点的机械性质与导电性值皆会大幅降低。若接点间隙过小,回焊过程 (Reflow Process) 中两相邻焊锡球容易碰触在一起,形成桥接失效 (Bridge Failure) 而导致芯片失效,且间距越小,填充底部的填充剂将会更加困难。即使能够微缩,焊锡与 IMC 的电阻率大约是铜的十倍,因此也不合适用于高性能组件封装。

图二 覆晶接合流程图

(a)未接合试片样子 (b)接点回焊后样子 (c)部填充剂填充过程 (d)填充完成后接点图[1]

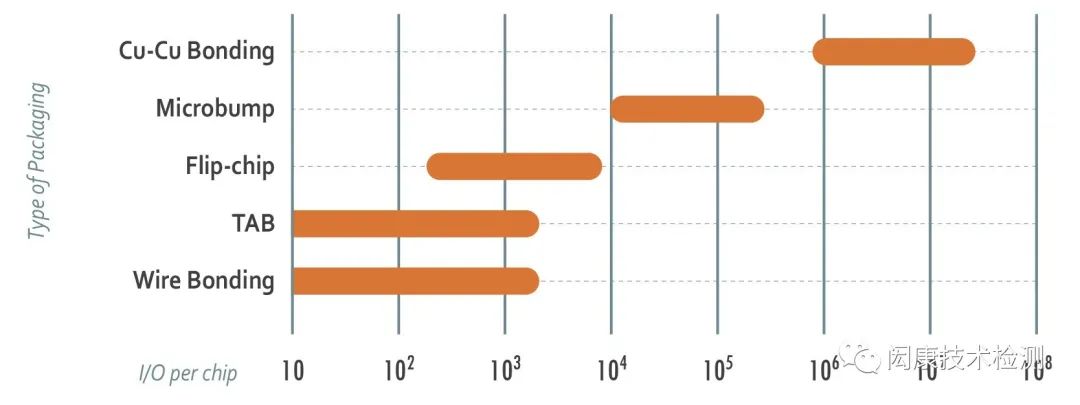

因此有学者提出利用铜-铜异质接合 (Cu-Cu Hybrid Bonding) 技术,将金属接点镶嵌在介电材料 (Dielectric Material) 之间,并同时利用热处理接合两种材料,利用铜金属在固态时的原子扩散来达到接合,故不会有 Bridging 问题。铜工艺是半导体业非常成熟的技术,铜-铜接点的间距可以微缩到 1 微米以下,因此在 1x1cm2 的芯片内,能够制作出超过一百万的接点,因此金属的直接接合变得非常重要。图三是各种封装技术在 1x1cm2 的芯片内能达到的接点数量[2]。

图三 各種封裝技術在 1x1cm2 的晶片內能達到的接點數量[2]

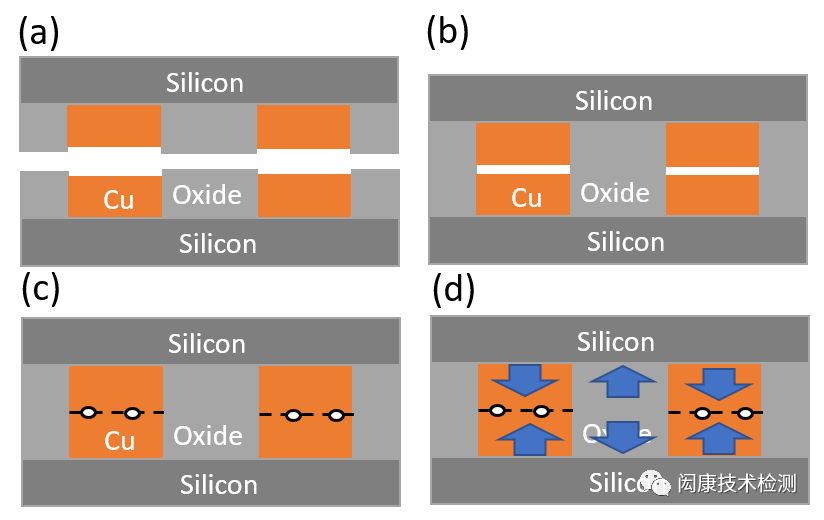

异质接合相较覆晶技术有三大优势,第一为可以达到超细间距与超小接点尺寸,故可以达到超高 I/O 数目;第二,由介电材料接合取代底部填充剂可以省去填充成本;第三,覆晶技术中,焊锡球会让芯片与基板或芯片中存在约 10 至 30 微米的厚度,异质接合则几乎没有厚度,未来发展的 3D 封装技术需要堆栈非常多层芯片,因此利用异质接合可以大幅减少总体厚度。最早由 Ziptronix 公司 (今 Xperi) 实现低温直接接合接点 (Direct Bond Interconnection, DBI) 的可行性[3],其接合步骤如图四所示。

首先,准备好芯片具有 SiO2 (介电材料) 与铜 (接点金属),此时铜部分将会有点略低于介电材料厚度,利用等离子 (Plasma) 做表面活化处理,将芯片面对面在室温下进行对位接合,由于凡德瓦力作用已具有一定的接合强度,接着在 100℃ 下持温让 SiO2 与 SiO2 之间进行缩合反应,形成强力共价键提高接合强度。接着再将温度提高到 300℃ 至 400℃ 持温,此时由于铜金属的热膨胀系数较 SiO2 来的大,铜表面将会碰触在一起,并自然受到一压应力,促使铜接点进行扩散接合。

根据研究学者指出,欲达到低温接合,介电材料层与金属层在经过化学抛光研磨后造成的高度差异将会是关键,研磨液与研磨参数的选择是导致不同厚度的主因,厚度差越小,便可于较低温度使铜表面接触并开始进行接合。

图四 异质接合流程图

(a)试片未接合样貌 (b)介电材料接合步骤 (c)提高温度铜接点接合过程 (d)高温时接点内部应力分布状态[3]

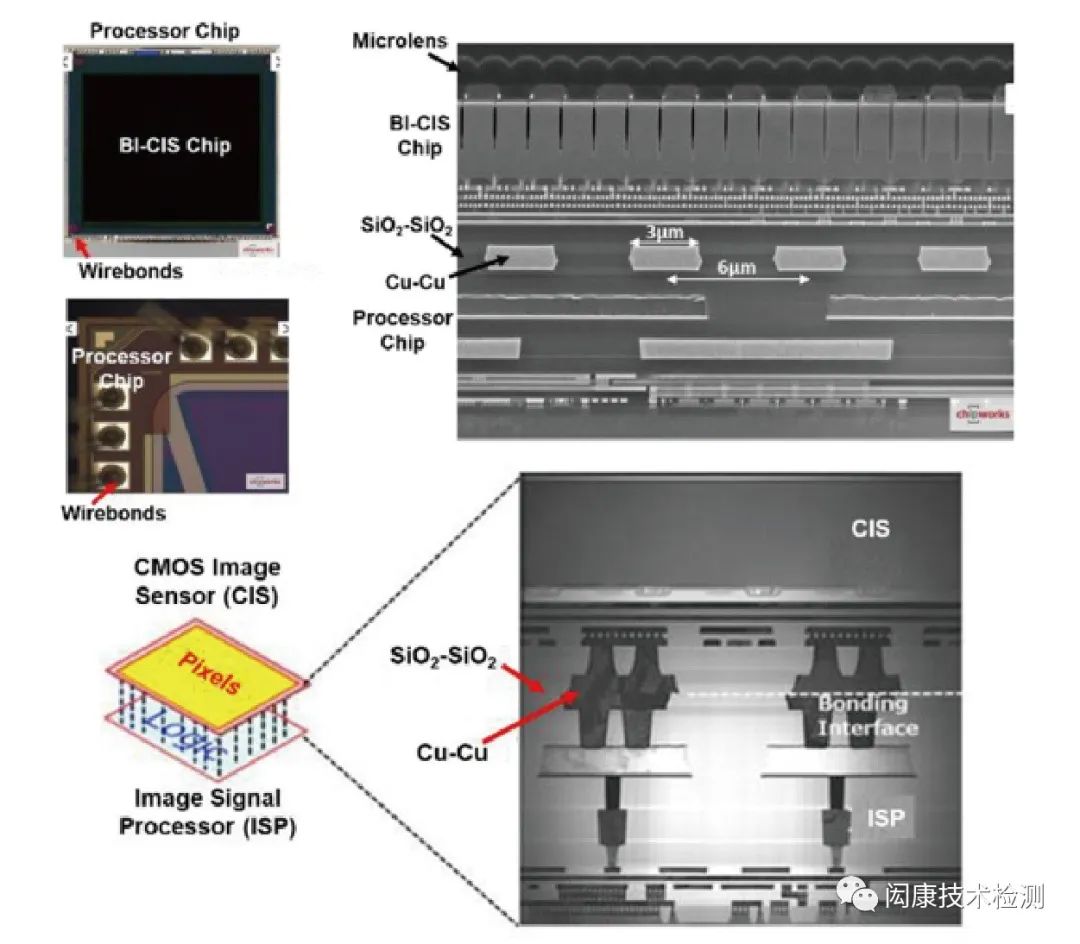

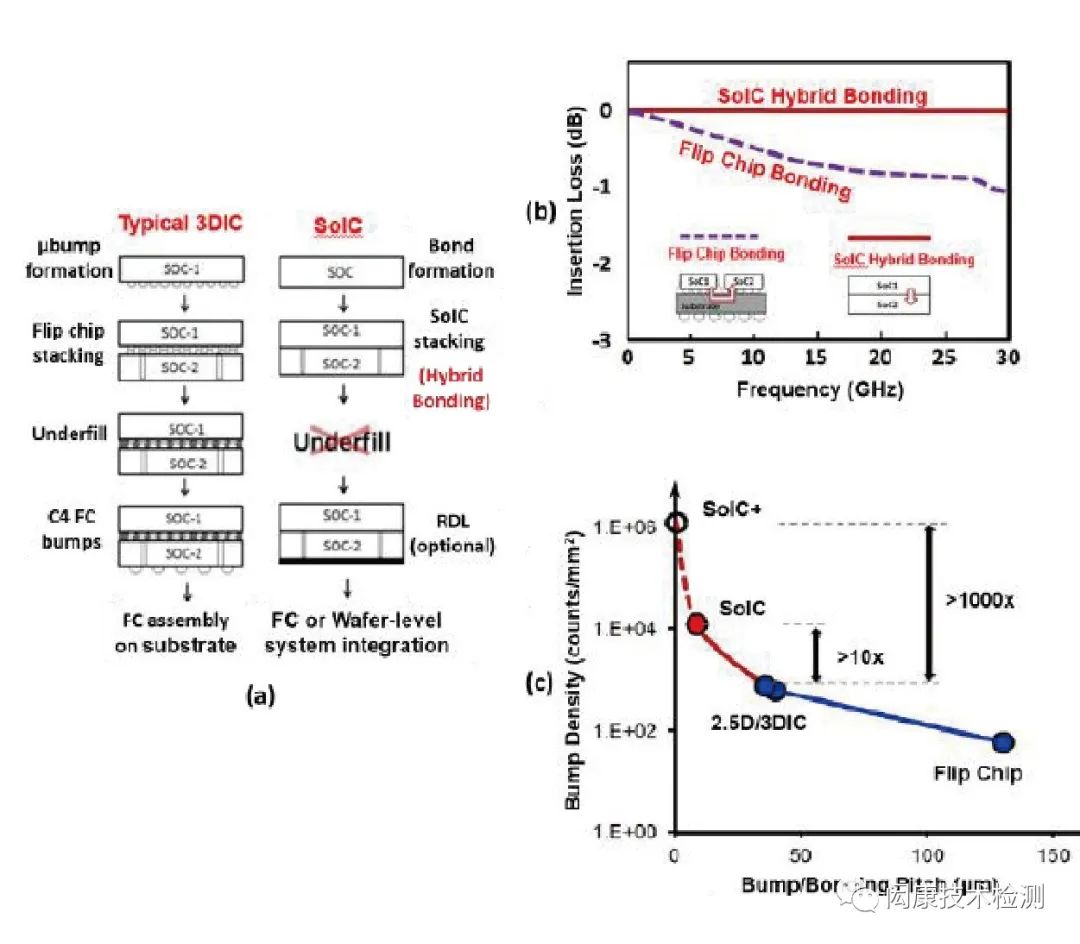

2016 年由 Sony 公司首先将异质接合技术应用在 Samsung Galaxy S7 的背照式 CMOS 影像侦测器 (Backside-illuminated CMOS Image Sensor, BI-CIS) 中,大幅提高了镜头分辨率,图五呈现出其横截面[4,5]。TSMC 则将此技术应用在系统整合芯片 (System on Integrated Chip, SoIC),图六呈现了 TSMC 目前研发 SoIC 的示意图[6,7],由图(b)可以发现在高频率下异质接合的 Insertion Loss 表现大幅优于传统覆晶焊锡接合,且接点数目可以由提升 10 倍至大于 1,000 倍以上,TSMC 竹南厂也将全力投入 3D-IC Heterogeneous Integration。

图五 Sony 用于 Samsung Galaxy S7 镜头 BI-CIS 利用异质接合接点横截面[4,5]

图六 TSMC 系统整合芯片 SoIC 示意图[6,7]

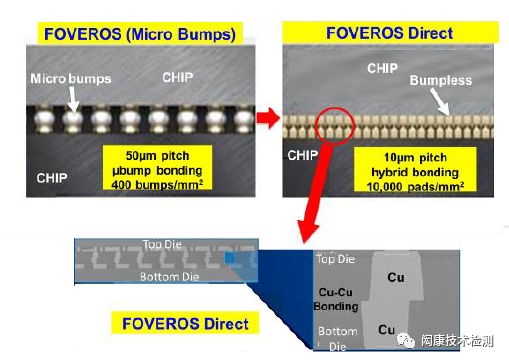

图七则呈现了 Intel 的异质接合研究成果[8],与覆晶接合技术相比,接点数目由每坪毫米 400 个提升至 10,000 个,未来持续将间隙缩小至 1 微米时,接点数目可达百万个。AMD 在 2021 年底介绍他们在 Server Processor 已经采用 TSMC 的 Cu/Oxide Hybrid Bonding 高密度封装技术,在 2022 年初亦宣布在高阶笔电的 Processer, Ryzen 7 5800X3D 也采用了 Hybrid Bonding 技术,将 7nm SRAM 迭接在 7nm Processor。比起使用焊锡 Microbumps,Cu Hybrid Bonding 能提升 200 倍的接点密度,而且每个讯号传递所需的能量降低至三分之一以下,非常令人惊艳。

图7 Intel 异质接合接点与微凸块焊锡接点横截面比较图

Hybrid Bonding 技术逐渐受到国际大厂的重视并列入 Roadmap 当中,除了上述例子之外,还有许多厂商如 IMEC, GlobalFoundries, Leti 等皆投入研究,其重要性不言而喻。

异质接合虽然具有大量优势,其生产成本仍然非常昂贵,如何透过优化接合条件以利于大量生产,台湾阳明交通大学陈智教授研究室携手闳康科技分析技术找到解方。

目前异质接合若要用于大量生产,需要晶圆对晶圆 (wafer to wafer, W2W) 对接之后再切削成小块,但 W2W 对于上下芯片的大小限制须为一样大小,否则将有区域浪费。近年来,有学者透过各种方法希望将接合温度与时间进一步降低,经过优化后的接合条件将有利于芯片对晶圆 (Chip to Wafer, C2W) 或是芯片对芯片 (Chip to Chip, C2C) 的大量生产。现阶段研究以 SiO2 为介电材料接合最为成熟,利用等离子的帮助即可达到低温接合,其他种的介电材料如 SiCN、高分子等材料,皆有学者在研究当中。亦有各大学者针对铜接点的接合机制与如何降低接合温度进行广泛研究,由于铜最大优点为相较其他金属材料便宜,并且具有良好的导电性、导热性与抗电迁移特性,未来必将成为重要的接点材料。但铜在高温下容易被氧化,表面具有氧化铜对于形成稳固的接点非常不利,目前一般的铜需要在适当真空 300℃ 至 400℃ 的环境中或是超高真空利用表面活化才能稳固接合,研究快速的铜铜直接接合接点对于大量生产非常重要。

目前铜接点最好用的方法为热压接合法 (Thermal Compression Bonding),为了达到低温接合,学者研究出了以下几种方法,第一种为接合前在铜接点表面镀上一钝化层 (Passivation Layer),防止铜氧化物生成来达到低温接合,常用的钝化金属有银[9]、金[10]与铂[11]等。另一种方式为改善接合表面扩散系数来达成低温接合。

2012 年本研究团队发现以直流电镀方式可以制备出纳米双晶铜[12],透过仪器分析其表面具有高度 (111) 的优选方向,在 2014 年报导利用高度 (111) 的优选表面在 150℃ 持温 60 分钟即可完成接合[13]。经过进一步的研究发现,具备高优选 (111) 表面的铜可以大幅提升表面的扩散系数,使铜接点可以在低温或短时间内将界面孔洞消除形成稳固的铜接点;并且由氧化实验中发现,表面为 (111) 方向时表面氧化物会较其它晶面少[14],其原因为在面心立方堆积结构中,(111) 晶粒表面有最少的断键,较不易生成氧化物。在 2019 年进一步将纳米双晶结构备制成铜凸块,并在 300℃、压力 90MPa 条件下只需要 10 秒即可以完成接点的接合,并且获得可靠的接点强度[15],将其称为瞬时接合 (Instant Bonding)。此接合条件虽然温度仍有点高,但可以在 10 秒内完成一个芯片的预接合对于未来 C2W 或是 C2C 接合将会有非常大的帮助,可以大幅减少接合成本。2021 年本研究团队也成功完成纳米双晶铜/SiO2 的异质接合[16],温度控制在 200 ℃ 即可以完成接合。

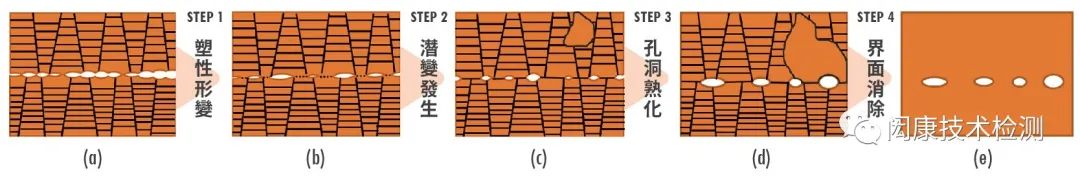

本研究团队将热压接合分成以下四阶段,每一阶段以孔洞的变化与铜接点微结构来区分,图八为四个阶段的流程图。

图八 接合步骤流程图

第一个阶段为「塑性形变」主导范围,初期铜接点表面有非常多的凹凸处,接触面积少,故施予的下压力非常容易超过金属的降伏强度 (Yield Strength),这些区域会在短时间内因塑性形变缩小接点间的间隙,此时接触部分应该会介于晶界与表面之间的一种状态,我们将之称为类晶界 (Quasi Grain Boundary),未接触的部分则会呈现不规则形状的孔洞。

第二阶段为由「潜变」主导的阶段,接合比例随着塑性形变发生而降低,其压应力会降至降伏强度以下,此时虽然低于降伏强度但是材料仍处于一个下压力,将导致接点的接合处与孔洞处产生应力梯度 (Stress Gradient),此应力梯度会让铜原子扩散并持续缩小孔洞大小,且表面铜原子与对面铜原子会开始形成金属键,让类晶界慢慢转变成为界面晶界 (Interfacial Grain Boundary)。2021 年本团队建置一个扩散模型,计算出了此阶段接合时间 (tbonding) 如式子 1 [17],由式子 1 可以知道接合时间与表面粗糙度 (Rq)、接合温度、下压力及有效扩散系数 (Deff) 有关系。由于接合机制在初期阶段是由表面扩散主导、而后期则转变成晶界扩散主导,此将使得有效扩散系数的数值大小界于表面扩散系数与晶界扩散系数之间。此外,当接合比例越来越大、或是转变成晶界扩散时,潜变形变速率将会大幅降低,且经过此阶段后,界面也将残留大小不一的孔洞。

接着进入第三阶段「孔洞熟化」(Void Ripening) 阶段,于此阶段开始出现较大孔洞成长与较小孔洞缩小的现象,原因是此阶段的孔洞为了降低整体能量,小孔洞具有较大的吉布斯自由能 (Gibbs free energy) 而较不稳定,空孔会由小孔洞沿着界面晶界往大孔洞移动,导致孔洞熟化现象发生,使平均孔洞尺寸变大[18]。

后一阶段为「界面消除」阶段,界面晶界受到晶粒成长影响而被消除掉,孔洞会被留在晶粒内部,空孔扩散的路径会由晶界扩散改变成晶格扩散 (Lattice Diffusion),致使空孔的扩散速度大幅下降,此时孔洞的大小将难以改变,其平均尺寸将不会有太大的变化。

接合后对于接点的分析非常重要,目前常见的非破坏分析方式为使用超音波扫描显微镜 (Scanning Acoustic Microscope, SAM) 来确认接合是否成功,藉由超音波穿透接合试片检查接点是否存在间隙,若有间隙存在则为接合失败区域,可再考虑以超高分辨率 3D X-Ray 显微镜来进一步接点观察。以上两种分析方法,其影像分辨率仅能达到数十微米至1微米左右。然而,在利用破坏性分析手法 (聚焦离子束) 初步观察后可以确认,实际接合界面会存在数十纳米的小孔洞,欲单纯采用非破坏性的分析方式,实难以观测到所有的界面孔洞。因此,目前对于接合面孔洞检测作法大多是采用破坏性分析。然而,此针对接点横切面进行电子显微镜影像分析之作法仍有不足之处,其能够观测到界面孔洞数量非常有限,无法真实呈现接合处的孔隙结果。

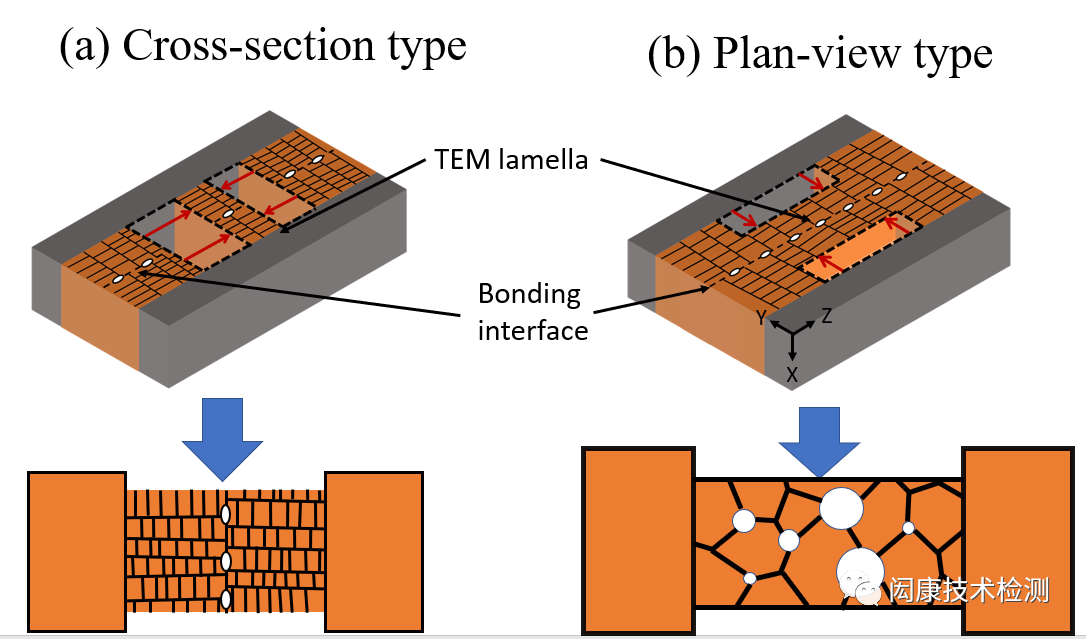

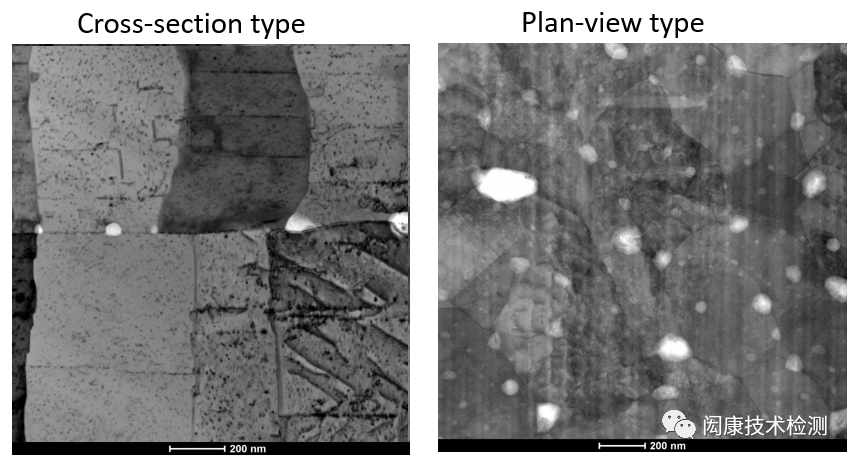

本团队与闳康科技 (Materials Analysis Technology Inc., MA-tek) 共同研发出新的铜接点界面观测方式,其中一种为使用穿透式电子显微镜 (TEM) 薄片备制方法、如图九所示,称之为 Plan-view Type。此作法首先将接合界面完整地挖出,整个薄片皆为接合界面,再利用电子显微镜观测及拍摄接合界面的俯视图,并测量统计界面孔洞的数量与大小。图十所示之影像范例是以 Plan-view Type 分析接合界面的实际结果。相比于一般横截面 (Cross-sectional Type) 作法,Plan-view Type 不仅可藉由观察界面俯视图,在小范围内观测到更大量的孔洞,并且能分析的孔洞尺寸范围也更大、约落在 10 至 100 纳米之间,此对于孔洞的研究帮助非常大。

图九 铜接点利用穿透式电子显微镜薄片备制方式观测孔洞两种方式

图十 相同条件铜接点利用穿透式电子显微镜薄片备制方式观测孔洞两种方式区别

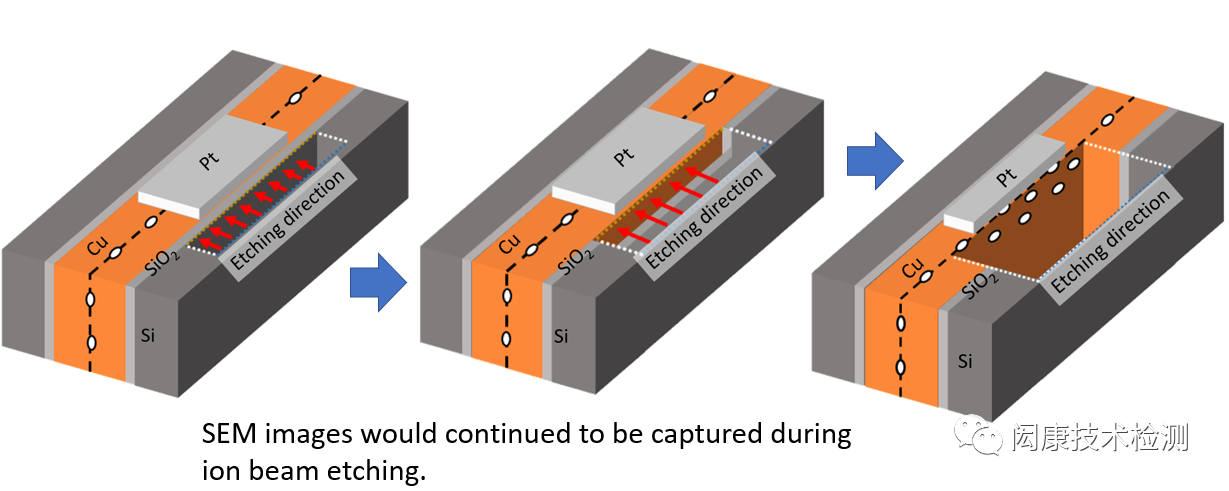

第二种方法为使用聚焦式离子显微镜系统搭配高分辨率扫描式电子显微镜来观测孔洞,我们称之为 Cut and View,分析作法如图十一所示。此方法较适合分析接合界面孔洞尺寸稍大 (至少大于 70 纳米) 的试片。随着离子束切削时扫描式电子显微镜持续拍摄,可以每隔一小段距离就拍摄一张照片,将所有照片制作成迭图后,即可以确认所有孔洞的数量与大小。以上两种分析方法在未来皆非常的重要,目前异质接合的接点尺寸可以小于 1 微米以下,因此对于接点的分析通常需要借助电子显微镜的帮助,而上述分析方式将可以有效地观察铜接点内部孔洞。

图十一 Cut and view 分析方式示意图

铜-铜异质接合技术可实现超高封装密度,并提供优异的导电与导热性质,预期在近年内它将会被大量地应用于高速计算组件中 (High Performance Computing)。然而,此技术工艺良率仍有待提升,并且其在结构可靠度方面,例如电迁移、温度循环测试等的相关研究数据也还不多,需要业界与学界共同投入更多的资源来加速发展。